- Current-carrying capacity of metal wire depends on cross-section. Height is fixed, so width determines current limit.

- Metal migration: when current is too high, electron flow pushes around metal grains. Higher resistance increases metal migration, leading to destruction of wire.

Modern VLSI Design 4e: Chapter 2

Copyright © 2009 Prentice Hall PTR

## Metal migration problems and solutions

- Marginal wires will fail after a small operating period infant mortality.

- » Under high currents, electron collisions with metal grains cause the metal to move; this process is called metal migration (also known as electromigration)

Copyright © 2009 Prentice Hall PTR

- Normal wires must be sized to accomodate maximum current flow:

- $I_{max} = 1.5 \text{ mA}/\mu\text{m}$  of metal width.

- Mainly applies to  $V_{DD}/V_{SS}$  lines.

Modern VLSI Design 4e: Chapter 2

|                                    |                          |                                 | process.                             |                           |                               |

|------------------------------------|--------------------------|---------------------------------|--------------------------------------|---------------------------|-------------------------------|

|                                    |                          |                                 |                                      |                           |                               |

| p-type transconductance            | k'p                      | -30µA/V <sup>2</sup>            | poly resistivity                     | R <sub>poly</sub>         | 8Ω/□                          |

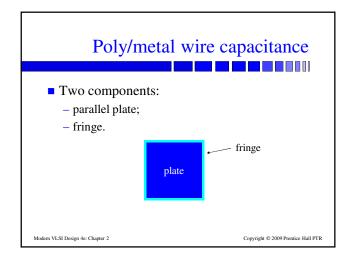

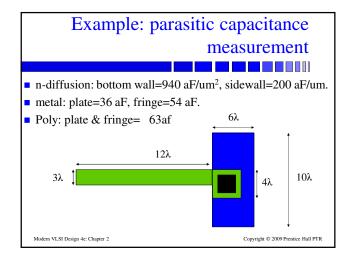

| n-type threshold voltage           | V <sub>tn</sub>          | 0.5V                            | metal 1-substrate plate capacitance  | Cmetal1,plate             | 36 <i>a</i> F/µm <sup>2</sup> |

| p-type threshold voltage           | V <sub>tp</sub>          | -0.5V                           | metal 1-substrate fringe capacitance | Cmetal1,fringe            | 54 <i>a</i> F/µm              |

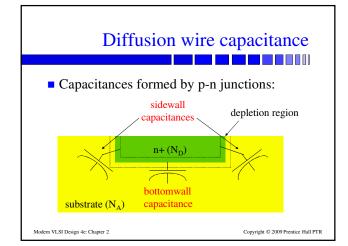

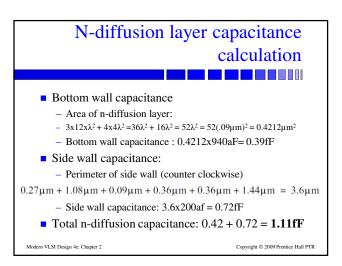

| n-diffusion bottomwall capacitance | Cndiff,bot               | 940 <i>a</i> F/µm <sup>2</sup>  | metal 2-substrate capacitance        | Cmetal2,plate             | 36 <i>a</i> F/µm <sup>2</sup> |

| n-diffusion sidewall capacitance   | C <sub>ndiff,side</sub>  | 200 <i>a</i> F/µm               | metal 2-substrate fringe capacitance | Cmetal2.fringe            | 51 <i>a</i> F/µm              |

| p-diffusion bottomwall capacitance | C <sub>pdiff,bot</sub>   | 1000 <i>a</i> F/µm <sup>2</sup> | metal 3-substrate capacitance        | C <sub>metal3,plate</sub> | 37 <i>a</i> F/µm <sup>2</sup> |

| p-diffusion sidewall capacitance   | C <sub>pdiff,side</sub>  | 200 <i>a</i> F/µm               | metal 3-substrate fringe capacitance | Cmetal3,fringe            | 54 <i>a</i> F/um              |

| n-type source/drain resistivity    | R <sub>ndiff</sub>       | $7\Omega/\Box$                  | metal 1 resistivity                  | R <sub>metal1</sub>       | 0.08Ω/□                       |

| p-type source/drain resistivity    | R <sub>pdiff</sub>       | 7Ω/□                            | metal 2 resistivity                  | R <sub>metal2</sub>       | 0.08Ω/□                       |

| poly-substrate plate capacitance   | C <sub>poly,plate</sub>  | 63 <i>a</i> F/µm <sup>2</sup>   | metal 3 resistivity                  | R <sub>metal3</sub>       | 0.03Ω/□                       |

| poly-substrate fringe capacitance  | C <sub>poly,fringe</sub> | 63 <i>a</i> F/µm                | metal current limit                  | I <sub>m.max</sub>        | 1mA/µm                        |

|                                    |                          |                                 | ire capacitance                      | ,                         | lmA/μm                        |