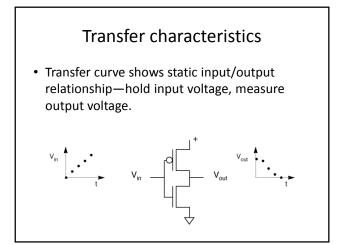

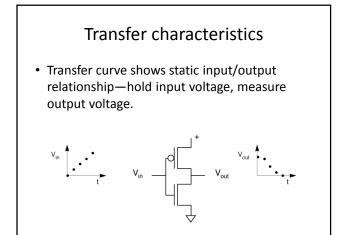

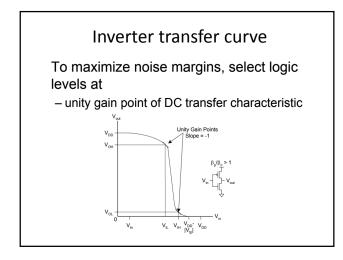

### Logic thresholds

- Choose threshold voltages at points where slope of transfer curve = -1.

- Inverter has a high gain between V<sub>IL</sub> and V<sub>IH</sub> points, low gain at outer regions of transfer curve.

- Note that logic 0 and 1 regions are not equal sized—in this case, high pullup resistance leads to smaller logic 1 range.

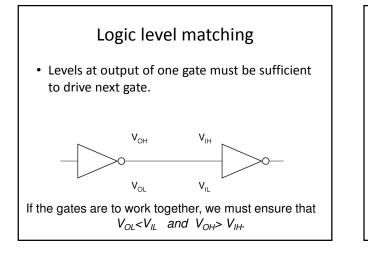

Noise margin = voltage difference between output of one gate and input of next. Noise must exceed noise margin to make second gate produce wrong output.

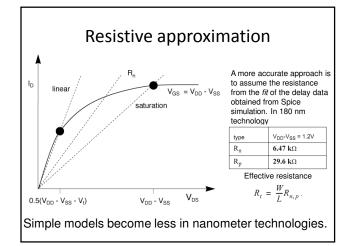

### Resistive model for transistor

• Average V/I at two voltages:

- maximum output voltage

- middle of linear region

- Voltage is V<sub>ds</sub>, current is given I<sub>d</sub> at that drain voltage. Step input means that V<sub>gs</sub> = V<sub>DD</sub> always.

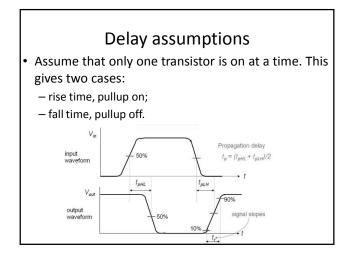

### Ways of measuring gate delay

- Delay: time required for gate's output to reach 50% of final value.

- Transition time: time required for gate's output to reach 10% (logic 0) or 90% (logic 1) of final value.

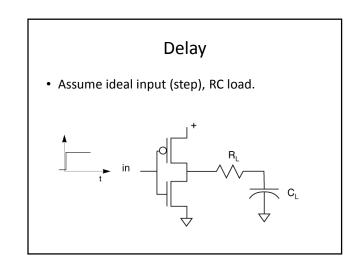

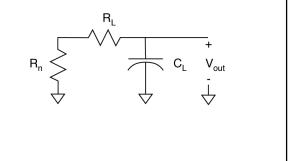

## Inverter delay circuit

• Load is resistor + capacitor, driver is resistor.

# Inverter delay with $\boldsymbol{\tau}$ model

- +  $\tau$  model: gate delay based on RC time constant  $\tau.$

- $V_{out}(t) = V_{DD} \exp{-t/[(R_n+R_L)C_L]}$

- t<sub>f</sub> = 2.2 R C<sub>L</sub>

- For pullup time, use pullup resistance.

# $\boldsymbol{\tau}$ model inverter delay

- 0.180 nm process:

- $-R_n$  = 6.47 k $\Omega$

- $C_{l} = 0.89 \text{ fF}$

- C<sub>L</sub> = 1.78 fF

- So

- t<sub>d</sub> = 0.69 x 6.47E3 x 1.78E-15 = 7.8 ps.

- $t_f = 2.2 \ x \ 6.47E3 \ x \ 1.78E-15 = 26.4 \ ps.$