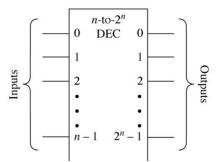

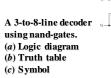

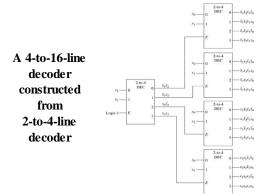

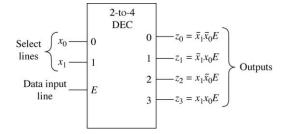

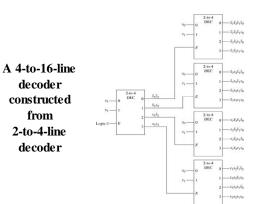

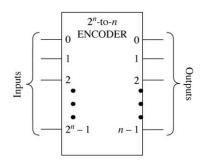

## An *n*-to-2*n*-line decoder symbol

Dept. of Computer Science and Engineering University of Rajshahi www.ru.ac.bd

**Dr. Shamim Ahmad**

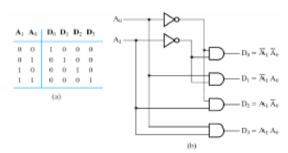

### 2-to-4 Decoder

### Decoder with enable: 2-to-4

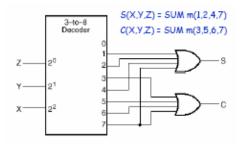

Implementing a Binary Adder Using a Decoder

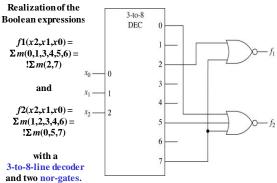

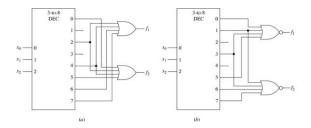

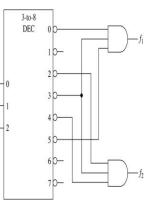

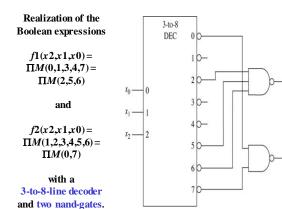

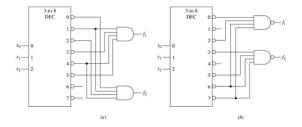

$f1(x2,x1,x0) = \Pi M(0,1,3,5)$  $f2(x2,x1,x0) = \Pi M(1,3,6,7)$ (*a*) Using output or-gates. (*b*) Using output nor-gates.

$f1(x2,x1,x0) = \Pi M(0,3,5)$ and  $f2(x2,x1,x0) = \Pi M(2,3,4)$

X0.

XI

$x_2 -$

with a 3-to-8-line decoder and two and-gates

A decoder realization of  $f1(x2,x1,x0) = \Sigma m(0,2,6,7)$  and  $f2(x2,x1,x0) = \Sigma m(3,5,6,7)$ (a) Using output and-gates. (b) Using output nand-gates.

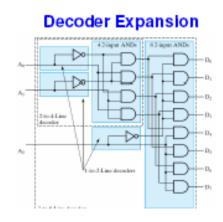

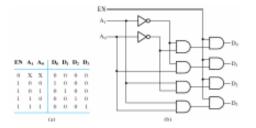

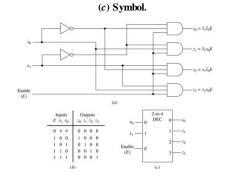

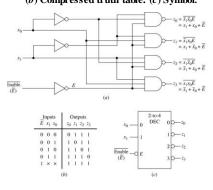

And-gate 2-to-4-line decoder with an enable input. (a) Logic diagram (b) Compressed truth table

Nand-gate 2-to-4-line decoder with an enable input (a) Logic diagram (b) Compressed truth table. (c) Symbol.

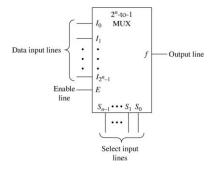

#### A 2n-to-1-line Multiplexer symbol

A 4-to-1-line multiplexer. (a) Logic diagram (b) Compressed truth table. (c) Symbol

| ſ | E | $S_1$ | <b>S</b> <sub>2</sub> | f              |

|---|---|-------|-----------------------|----------------|

| Ī | 0 | х     | x                     | 0              |

|   | 1 | 0     | 0                     | I <sub>0</sub> |

|   | 1 | 0     | 1                     | $I_1$          |

|   | 1 | 1     | 0                     | $I_2$          |

|   | 1 | 1     | 1                     | I <sub>3</sub> |

# A Multiplexer tree to form a 16-to-1-line Multiplexer

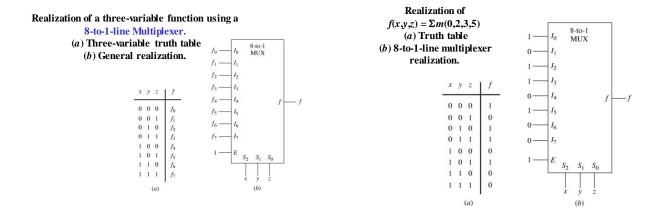

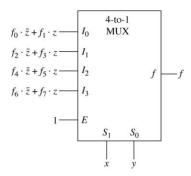

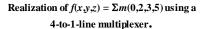

#### A general realization of a 3-variable Boolean function using a 4-to-1-line multiplexer.

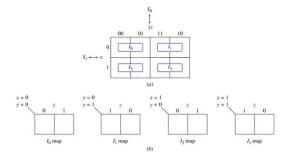

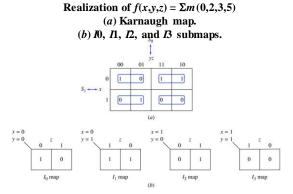

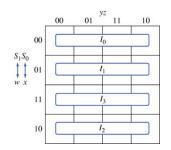

Obtaining multiplexer realizations using Karnaugh maps. (a) Cell groupings corresponding to the data line functions. (b) Karnaugh maps for the *Ii* subfunctions

Using Karnaugh maps to obtain multiplexer realizations under various assignments to the select inputs.

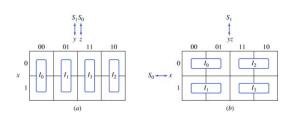

(a) Applying input variables y and z to the S1 and S0 select lines. (b) Applying input variables x and y to the S0 and S1 select lines.

Alternative realizations of  $f(x,y,z) = \Sigma m(0,2,3,5)$ . (a) Applying input variables y and z to the S1 and S0 select lines. (b) Applying input variables x and y to the S0 and S1 select lines.

#### A selectline assignment and corresponding data line functions for a multiplexer realization of a four-variable function.

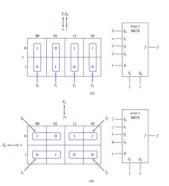

S<sub>0</sub> 8-to-1 MUX t  $I_0$ yz  $I_1$ 00 01 11 10 1,  $I_3$ 0 00 0  $I_4$ 15  $S_2S_1 \xrightarrow{01}_{w x} S_1$ 0  $I_6$ I-0 1 0 S 10 0 0 0 (*a*) (b)

Realizations of  $f(w,x,y,z) = \Sigma m(0,1,5,6,7,9,12,15)$

(a) Karnaugh map. (b) Multiplexer realization.

Using a four-variable Karnaugh map to obtain a Boolean function realization with a 4-to-1-line multiplexer.

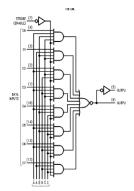

Order Number 54151ADMQB, 54151AFMQB, DM54151AJ, DM54151AW or DM74151AN See NS Package Number J16A, N16E or W16A

## Demultiplexer.

## Encoders

#### Encoder Example

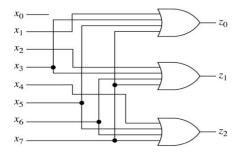

· Example: 8-to-3 binary encoder (octal-to-binary)

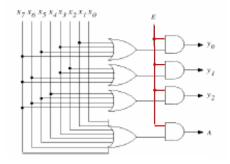

### An 8-to-3-line encoder.

### Encoder Example (cont.)

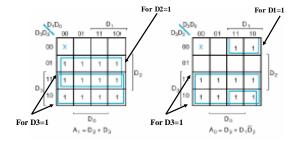

## 4-to-2 Priority Encoder (cont.)

• The operation of the priority encoder is such that:

- If two or more inputs are equal to 1 at the same time, the

input in the **highest-numbered** position will take precedence.

• A *valid output indicator*, designated by V, is set to 1 only when **inputs one or more** are equal

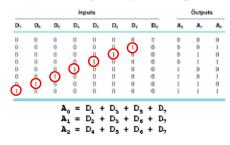

#### Example: 4-to-2 Priority Encoder Truth Table

| Inputs       |                |                |                  | Outputs |    |   |  |

|--------------|----------------|----------------|------------------|---------|----|---|--|

| D3           | $\mathbf{D}_2$ | $\mathbf{D}_1$ | $\mathbf{D}_{0}$ | А,      | Aa | v |  |

| 0            | 0              | 0              | 0                | х       | х  | 0 |  |

| 0            | 0              | 0              |                  | 0       | 0  | 1 |  |

| )            | -0             |                | X                | 0       | 1  | 1 |  |

| 0            |                | X              | X                | 1       | 0  | 1 |  |

| $\mathbf{D}$ | X              | x              | X                | 1       | 1  | 1 |  |

Example: 4-to-2 Priority Encoder K-Maps

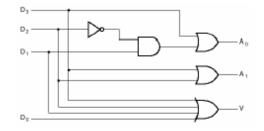

Example: 4-to-2 Priority Encoder Logic Diagram

**Priority Encoders**

|    | -  | -  | -  |    | -  | _  |    | -  |    | -  | - |

|----|----|----|----|----|----|----|----|----|----|----|---|

| x0 | x1 | x2 | x3 | x4 | x5 | xб | x7 | z2 | z1 | z0 | V |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 |

| 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1 |

| Х  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1 |

| Х  | Х  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1 |

| Х  | X  | X  | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1 |

| Х  | Х  | X  | Х  | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 1 |

| Х  | Χ  | X  | Х  | Х  | 1  | 0  | 0  | 1  | 0  | 1  | 1 |

| Х  | Х  | X  | Х  | Х  | Χ  | 1  | 0  | 1  | 1  | 0  | 1 |

| Χ  | Х  | X  | Х  | Х  | Х  | Х  | 1  | 1  | 1  | 1  | 1 |

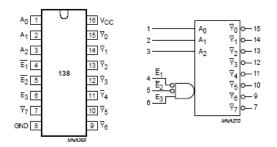

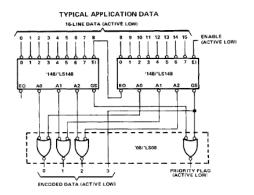

'148. 'LS148

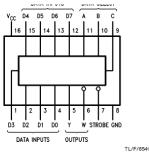

| 4     | h  | $U_{16}$ | Vcc  |

|-------|----|----------|------|

| 5 🗌   | 2  | 15       | ] E0 |

| 6     | 3  | 14       | GS   |

| 70    | 4  | 13       | 3    |

| EL    | ļs | 12       | 2    |

| A2 [  | 6  | 11,      | 1    |

| A1 C  | 17 | 10       | 0    |

| GND [ | ]в | 9        |      |

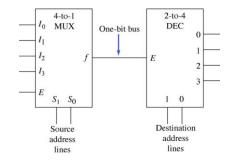

A multiplexer/demultiplexer arrangement for information transmission