## Gate design...

- We must work with both logic expressions and gate networks to find the best implementation of a function, *keeping in mind*:

- combinational logic expressions are the specification;

- logic gate networks are the implementation;

- area, delay, and power are the costs.

Modern VLSI Design 4e: Chapter 3

Copyright © 2008 Wayne Wolf

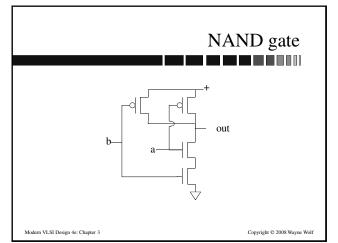

## Completeness (*universality*)

- A set of functions *f1*, *f2*, ... is complete (universal) if every Boolean function can be generated by a combination of the functions.

- Complete (universal): NAND, NOR

- AND, OR are not complete.

If your set of logic gates is not complete, you can't design arbitrary logic.

Modern VLSI Design 4e: Chapter 3

Copyright © 2008 Wayne Wolf

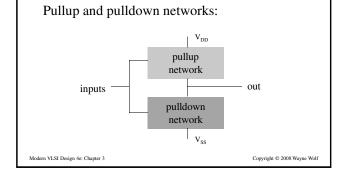

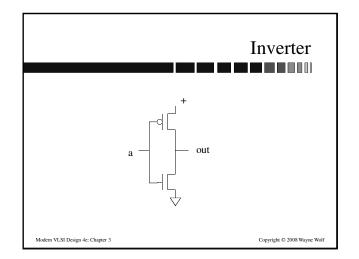

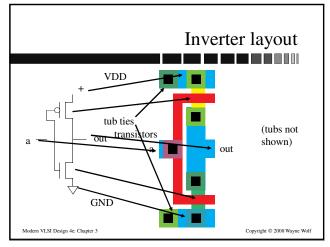

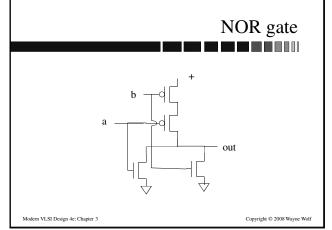

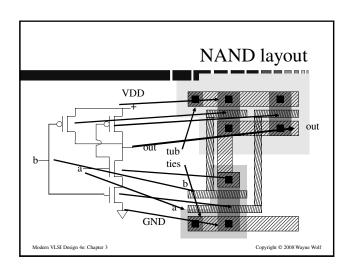

One family of logic gate circuits: the *static complementary gate*

- *Complementary*: have complementary pullup (p-type) and pulldown (n-type) networks.

- *Static*: do not rely on stored charge.

- Simple, effective, reliable; hence ubiquitous.

Modern VLSI Design 4e: Chapter 3

Copyright © 2008 Wayne Wolf

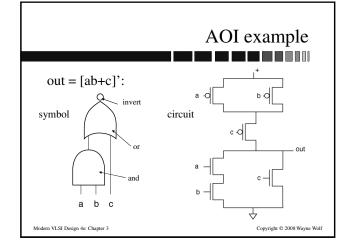

- AOI = and/or/invert; OAI = or/and/invert.

- Implement larger functions.

- Pullup and pulldown networks are compact: smaller area, higher speed than NAND/NOR network equivalents.

- AOI312: AND 3 inputs, AND 1 input (dummy), AND 2 inputs; OR together these terms; then invert.

Modern VLSI Design 4e: Chapter 3

Copyright © 2008 Wayne Wolf

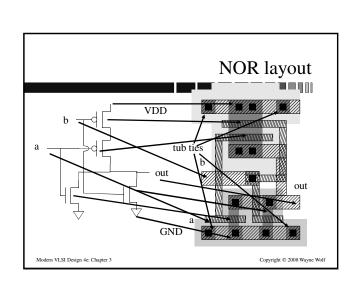

## Pullup/pulldown network design

- Pullup and pulldown networks are duals.

- To design one gate, first design one network, then compute dual to get other network.

- Example: design network which pulls down when output should be 0, then find dual to get pullup network.

Modern VLSI Design 4e: Chapter 3

Copyright © 2008 Wayne Wolf