## Layout Design

- Layouts are very detailed and designing them can be very tedious and difficult.

- Layout abstractions and methodologies to help us design layouts.

Modern VLSI Design 4e: Chapter 2

Copyright © 2008 Prentice Hall PTR

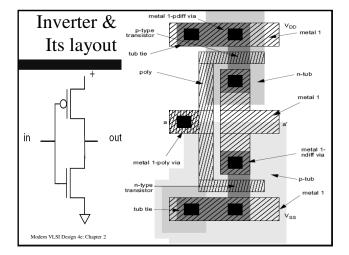

Layout is drawn considering,

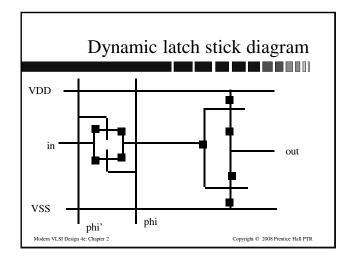

- Vias are used to go from n-diff to metal and then to p-diff.

- The *in* signal is naturally in polysilicon, but the *out* signal is naturally in metal, since we must use a metal strap to connect the transistors' source and drain.

- Metal is used for the power and ground connections.

Modern VLSI Design 4e: Chapter 2

Copyright © 2008 Prentice Hall PTF

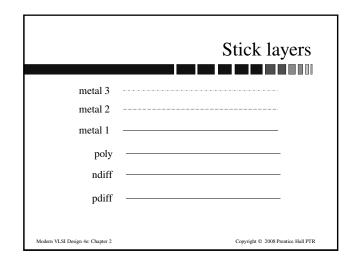

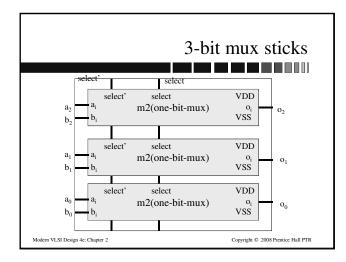

## Stick diagram: Abstraction of layout

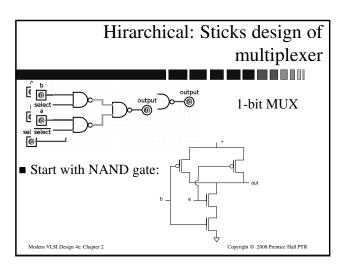

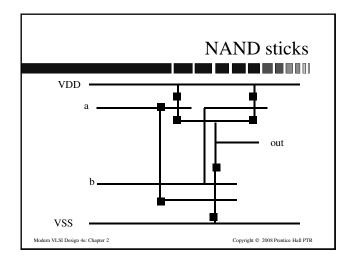

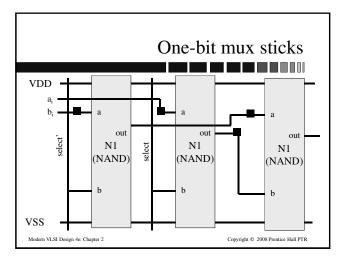

- A stick diagram is a cartoon of a layout.

- Does show all components/vias (except possibly tub ties), relative placement.

- Does not show exact placement, transistor sizes, wire lengths, wire widths, tub boundaries.

Modern VLSI Design 4e: Chapter 2

Copyright © 2008 Prentice Hall PTR

## Layout design and analysis tools

- Layout editors are interactive tools.

- Design rule checkers are generally batch---identify DRC errors on the layout.

- Circuit extractors extract the netlist from the layout.

- Connectivity verification systems (CVS) compare extracted and original netlists.

Modern VLSI Design 4e: Chapter 2

Copyright © 2008 Prentice Hall PTR

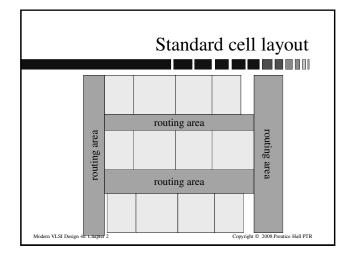

## Automatic layout

- Cell generators (macrocell generators) create optimized layouts for ALUs, etc.

- Standard cell/sea-of-gates layout creates layout from predesigned cells + custom routing.

- Sea-of-gates allows routing over the cell.

Modern VLSI Design 4e: Chapter 2

Copyright © 2008 Prentice Hall PTR